2章では、内部端子とレジスタについて解説します。

内部端子とレジスタは表8の宣言コマンドを使用します。

| 【表2-1.内部端子・レジスタのコマンド表】 | |

| 宣言の種類 | 意味 |

| wire reg | 内部端子 レジスタ |

2-1.内部端子の解説

内部端子は配線の役割をする構文です。

一つの信号を複数に増やしたり、演算の補助をする目的に使います。

内部端子に転送した値は、転送した時と同クロックで使用可能です。

そして、内部端子に値を何も転送しない間は、値が定らない状態(不定)になります。

内部端子の宣言方法は以下の様に行います。

wire 内部端子名 [ビット幅]

ビット幅は省略可能で、省略した場合は1ビットに決定します。

また、wireに値やデータを代入する場合は”=”を使って以下の様に記述します。

内部端子名 = 値

内部端子の使用例として、例題3を見てみましょう。

| 【例題3.内部端子の使用例】 |

declare ex03 { |

この例題3は”データ端子の宣言”, “内部端子の宣言”,

“共通アクション記述”,を有するモジュールです。

ハードウェア記述言語は並列動作を行うので、 共通アクション記述に記述した複数の動作は同時に実行します。

例題3の式1は「内部端子cに、”a”と”bの否定”の論理積を代入する」という動作です。

次に、式2は「内部端子dに、”aの否定”と”b”の論理積を代入する」という動作です。

そして、式3は「データ出力端子fに、c,dの論理和を代入する」という動作です。

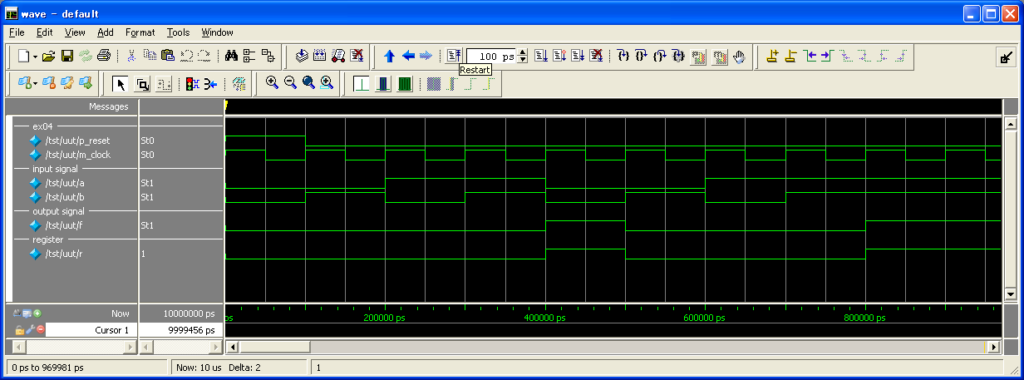

例題3のシミュレーション結果は以下の様になります。

2-2.レジスタ

レジスタはクロック信号の立ち上がりにおいて、

直前の入力値を記憶する記憶素子です。

レジスタの宣言方法は以下になります。

reg レジスタ名 = 初期値

初期値は省略可能です。

また、初期値の値はVerilog-HDL互換、C言語互換の他に

10進数の自然数を入力することも可能です。

動作記述でレジスタに値を代入する場合は、

データ端子やwireと違う記号”:=”を用いて以下の様に記述します。

レジスタ名 := 値

レジスタに代入した値は、代入した次のクロックで記憶されます。

そして、レジスタの値を代入する場合は代入記号”=”を使います。

信号名 = レジスタ名

レジスタの使用例として例題4を見てみましょう。

| 【例題4.レジスタ使用例】 |

declare ex04 { |

この例題4の式1は「レジスタrにa,bの論理積を代入する」という動作です。

そして、式2は「データ出力端子fにレジスタrを代入する」という動作です。

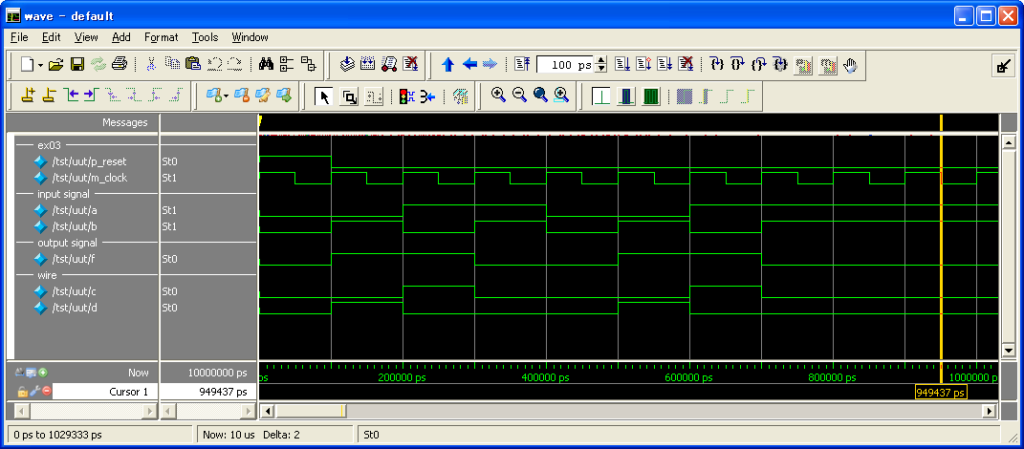

以下に論理シミュレーション結果を示します。